Creating a World where a 14-year-old Designs a Chip

> Mohamed Kassem Cofounder & CTO, EFABLESS.COM mkk@efabless.com

Main hattery

**Kindle Fire HD**

Motorola - Droid Bionic

Droid X

efah

Mohamed

Huawei Ascend D1

Motorola - Droid Milestone

## I break other stuff

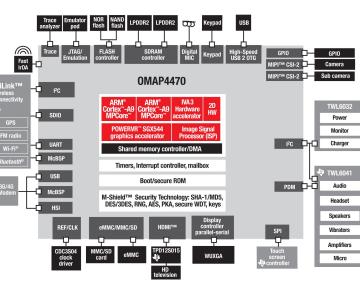

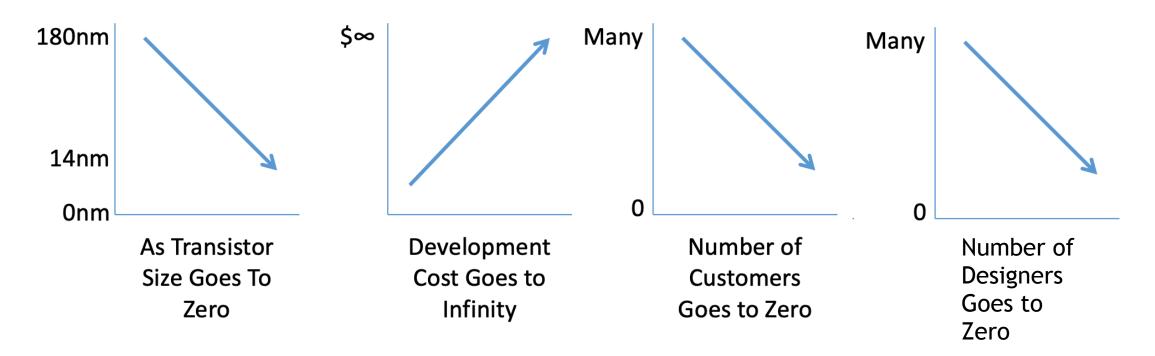

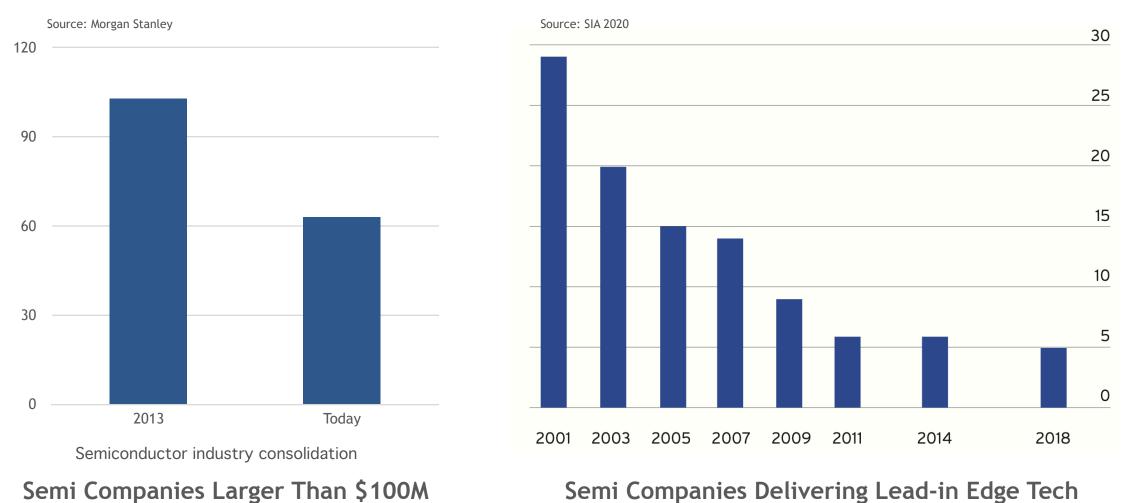

#### **INDUSTRY CHALLENGES**

Why is chip design and making has become less accessible to the world and stifling innovation?

#### **CHIP INDUSTRY TRENDS**

Source: Mike Noonen

#### **CHIP INDUSTRY TRENDS**

Semi Companies Delivering Lead-in Edge Tech

#### WE NEED A 1000X PRODUCT DEVELOPERS

Long-tail Innovation is required on a massive scale to meet demand 10,000's of Products

sales **Right-sized** Niche Extreme AI Ideation ML compute & power Solutions Markets number of products

**Markets Served**

**By Traditional**

Methodology

Creating a World where a 14-year-old Designs a Chip

## What about that?

## "In the beginner's mind there are many possibilities, but in the expert's there are few"

— Shunryu Suzuki, Zen Monk 1904-1971

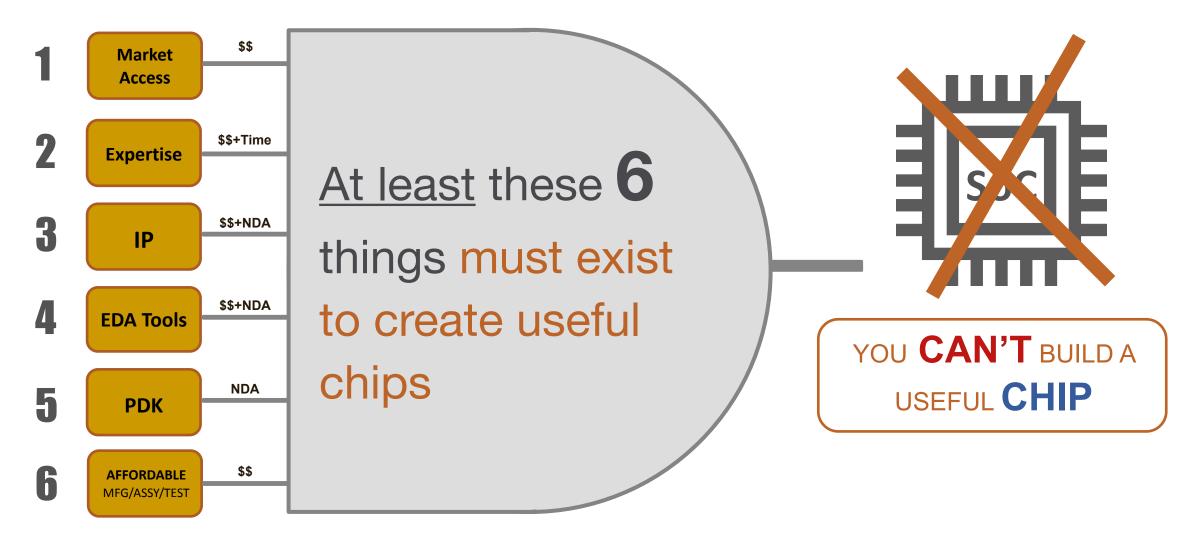

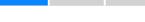

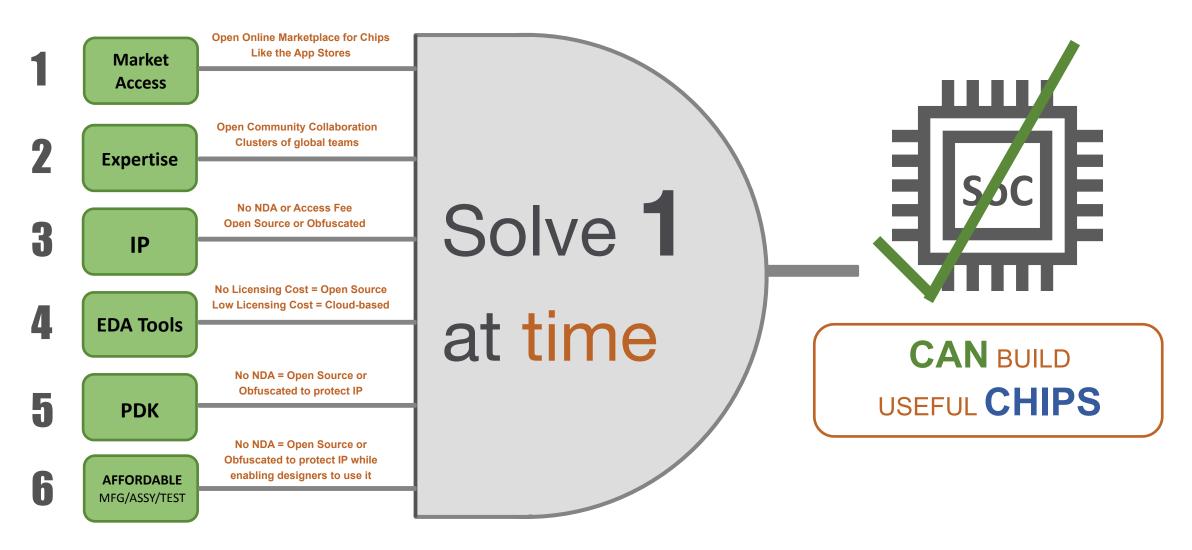

## Why is it "hard" to design chips

#### Limited access to knowledge

#### Limited access technology

#### Costly manufacturing

# Too many things to bring together ..... too complicated

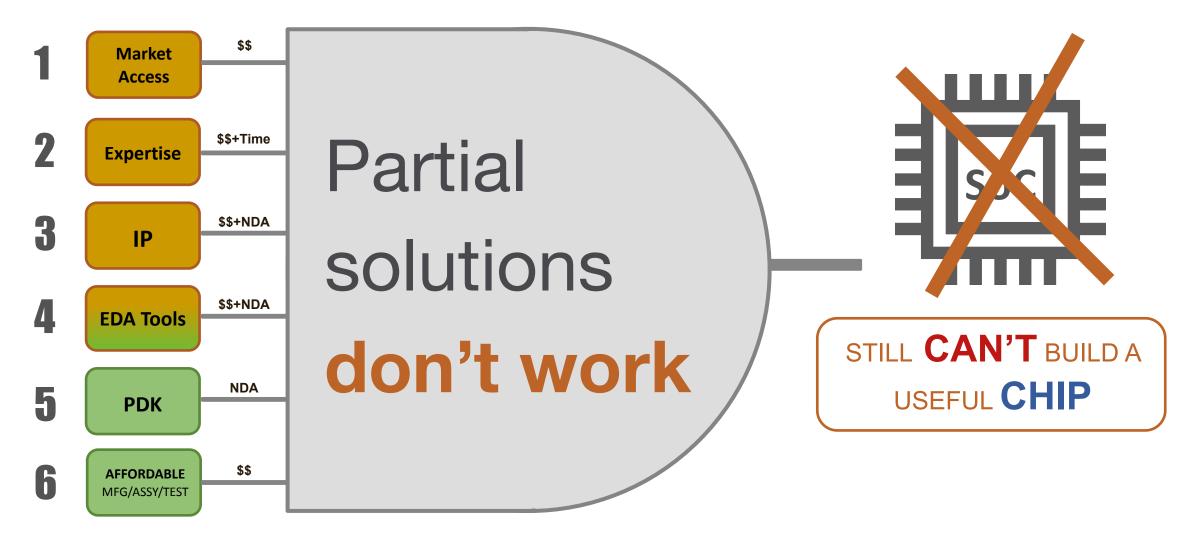

#### ..... too complicated

#### ..... still too complicated

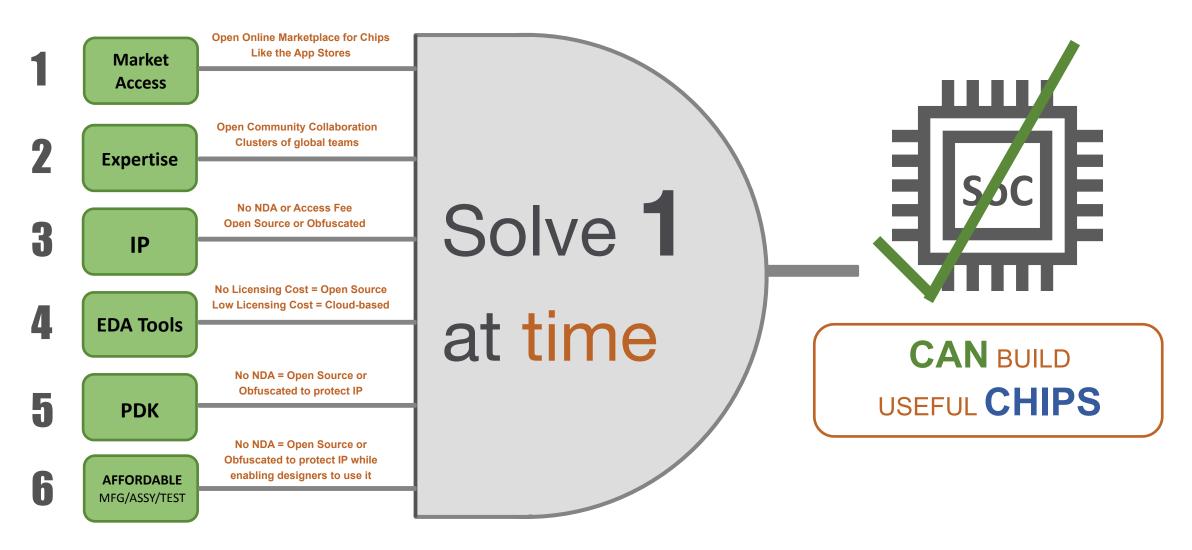

#### We need to

## Simplify the process of Chip creation and Open it to Everyone

© 2022 EFABLESS CORPORATION

## How would we simplify chip

design?

Think what **app stores** did to software innovation.

#### **Simplified** (democratized)

the development tools

the business process

the connection to customers

Think what app stores did to software innovation.

#### **Simplified** (democratized)

the **development tools** the **business process** the connection to customers

At least

Including kids

Think that we apply the same approach to chip design

#### **Simplify** (democratize)

the access to chip design tools & PDK

#### the **business process**

#### the connection to customers

Think that we apply the same Thousands approach to chip design

**Simplify** (democratize)

the **access** to chip design tools & PDK Millions

the **business process**

the connection to customers

Including kids

At least

#### .... what we need ...

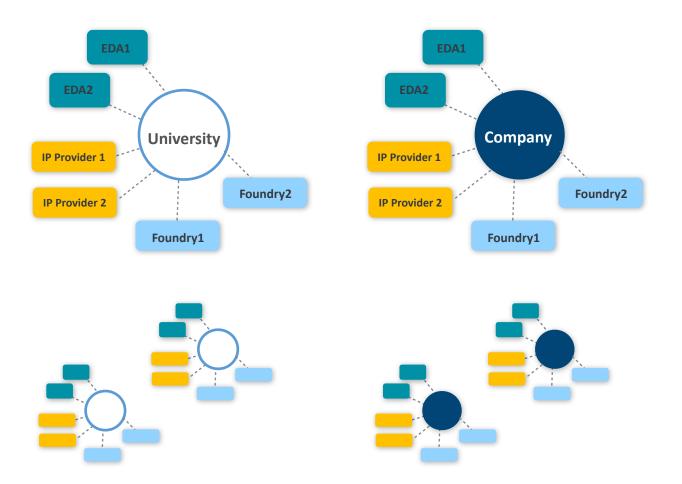

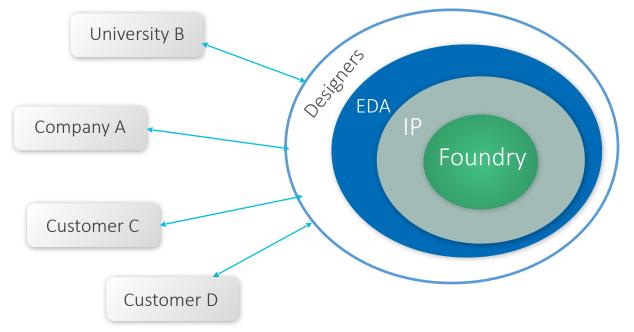

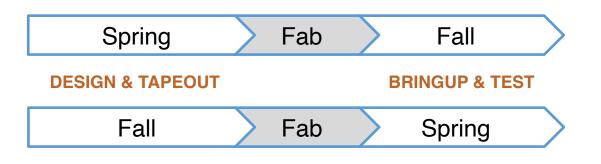

#### TODAY'S APPROACH

Every design entity needs to establish independent business and contractual (including NDA's) relationships with multiple

IP providers, EDA vendors,

and foundries

#### CLOUD - BUT NOT FOR COMPUTE

Secure, cloud-based platforms, all the resources and processes required to design ASICs and IP are offered in one place while maintaining the "fire-walling" of IP information and with enhanced traceability and on-demand elasticity.

Enabling a worldwide network of developers and customers to collaborate, model, and verify custom SoCs. When custom SoC creation becomes less risky and more cost-effective, innovation is unleashed.

Scalable & elastic design/development capacity

Facilitates Collaboration, reference designs and design re-use accelerates development and reducing costs

Risk reward sharing enabled by consolidated contribution tracking and design obfuscation

#### FOUNDRY DATA OBFUSCATION

Mask-geometry layout is foundry proprietary.

How can you design an entire chip and submit to the foundry for fabrication without signing an NDA, purchasing commercial tools, and installing PDKs?

All analog cells at the transistor level are abstracted views using information from the corresponding LEF files and simulation models

3.3V ADC, Original vendor layout:

(Layout blurred to protect the identity of the victim)

3.3V ADC, Abstracted layout (from LEF view):

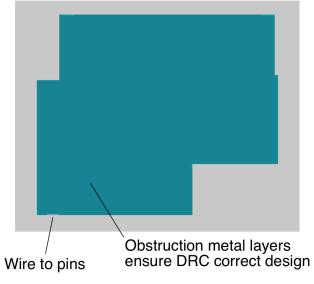

#### DESIGN IP OBFUSCATION

The target process: **X-FAB XH018** Base MOS LP (low power) option 6 metal stack (5 standard route layers, 1 thicker top

The proprietary data:

X-FAB digital standard cells

X-FAB I/O Cells(3.3V with both 3.3V and 1.8V core)

X-FAB Analog IP

X-FAB SRAM (from memory compiler)

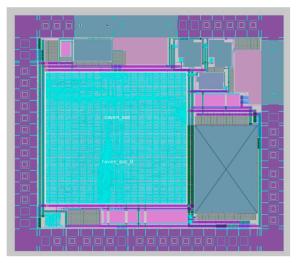

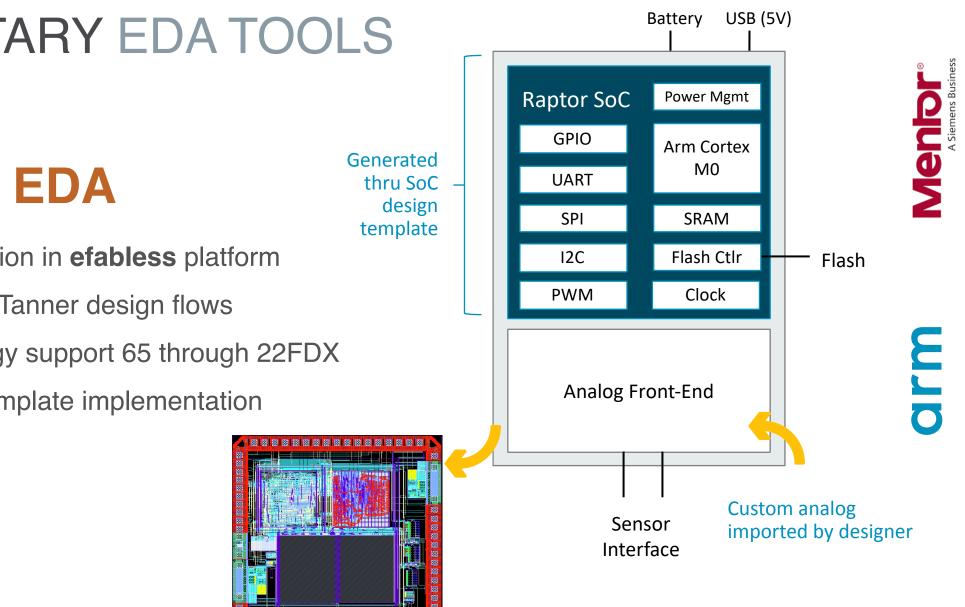

#### SIEMENS EDA

- Seamless integration in **efabless** platform

- Complete Mentor/Tanner design flows

- Process technology support 65 through 22FDX

- Optimized SoC template implementation

#### **KEY PLATFORM FEATURES**

- Instant access to the platform less than 5 minutes

- Option for No-NDA Access To Foundry Process Technology efabless' obfuscation technology

- No Upfront Cost Microelectronics Design Tools (EDA) using proven Open Source & Proprietary SW

- No IP licensing cost for prototyping enabled by IP obfuscation

- No cost Try Before Use/Buy for proprietary designs while protecting IP information and ownership

- Low cost prototype manufacturing options as multi-project-wafers (MPW) including bench setup

- Built-in project collaboration, forums and management enabling effective knowledge exchange

- Provides results-based reputation/certification indicators based on real user design performance

- Supports online **project-based** design, verification & validation of microelectronics

- Elastic and scalable infrastructure to support 10,000's of users

- Marketplace **connecting** designers to potential customers for their **unique design innovation**

## How do we simplify chip

# design? #1

© 2022 EFABLESS CORPORATION

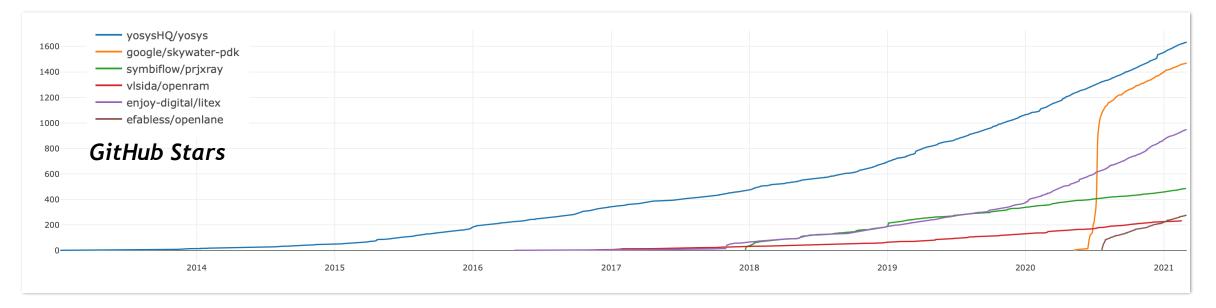

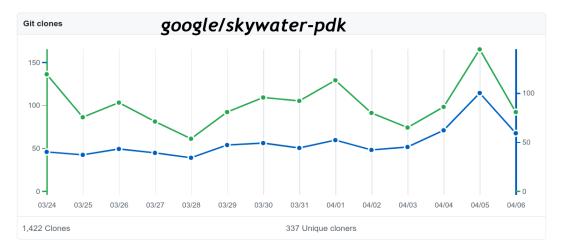

No NDA, nothing to sign - it's Open Source

\$ git clone https://github.com/google/skywater-pdk

Technology information availability is virtually limitless Leading to massive open collaboration

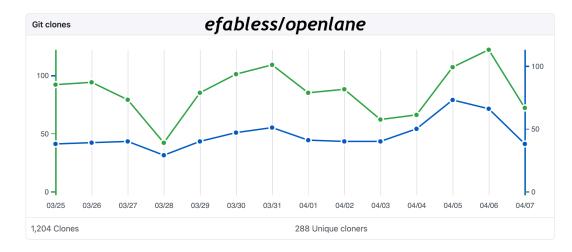

#### SKY130 OPEN SOUCRE PDK WENT VIRAL

#### LIVE COMMUNITY SLACK SPACE

**2,800+** COMMUNITY MEMBERS

#### **100+** CHANNELS & TOPICS

Join SkyWater-PDK Community https://join.skywater.tools

| •••      | $\leftarrow \rightarrow \bigcirc$ | Q Search skywater-pdk 🕖                                                                                                                                                                                                                       |

|----------|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>*</b> | skywater-pdk ~                    | # shuttle ~ mpw3 tags: OpenLANE: efabless/op     & 418                                                                                                                                                                                        |

| <b>A</b> | eeta                              | J Javier Contreras Sunday, September 19th ~<br>joined #shuttle along with 2 others.                                                                                                                                                           |

|          | # efabless                        | Wednesday, September 22nd ~                                                                                                                                                                                                                   |

| FOSS THE | A fabulous                        | wednesday, September 22nd V                                                                                                                                                                                                                   |

| _        | # fuserisc                        | matt venn 5:09 AM                                                                                                                                                                                                                             |

| •        | # general                         | who made the masks for us? Is that something that Skywater<br>organised? Or does efabless send the GDS to a mask factory fi<br>I'm asking because I'm researching this trojan hardware hack th<br>requires making modifications to the masks. |

|          | A ieee-sscs                       |                                                                                                                                                                                                                                               |

|          | # ieee-sscs-dc-21q3               |                                                                                                                                                                                                                                               |

|          | # images                          | If someone hacked a foundry would they be able to change the file                                                                                                                                                                             |

|          | # junk                            | that define the mask before they are fabricated?                                                                                                                                                                                              |

|          | # magic                           | Or would the hacker have to hack the mask factory?                                                                                                                                                                                            |

|          | # microwatt                       | Tim Edwards 5:45 AM                                                                                                                                                                                                                           |

|          | 合 mpw-one                         | @matt venn: Masks are made by a third party, but that's between                                                                                                                                                                               |

|          | # mpw-one-clean-short             | SkyWater and the mask house, and I don't know who their mask                                                                                                                                                                                  |

|          | # mpw-one-silicon                 | manufacturer is, other than that they tell us when they've started.                                                                                                                                                                           |

|          | 🔒 mpw-two                         | would guess that the trojan attack scenario assumes that it is an<br>"insider job" at the mask house, or something like that. The                                                                                                             |

|          | # openlane                        | scenario is rather implausible.                                                                                                                                                                                                               |

|          | # openram                         | 👍 1 😅                                                                                                                                                                                                                                         |

|          | # openroad                        | matt venn 5:46 AM                                                                                                                                                                                                                             |

|          | # private-shuttle                 | Maybe more plausible that the foundry is bribed to alter the mask                                                                                                                                                                             |

|          | # riscv                           | before sending                                                                                                                                                                                                                                |

|          | # shuttle                         | But yeah                                                                                                                                                                                                                                      |

|          | # shuttle-precheck                | Amro Tork 6:11 AM                                                                                                                                                                                                                             |

|          | # silicon-validation              | @matt venn In my other life, we used to get the Mask files and                                                                                                                                                                                |

|          | # sky130                          | check them using an automated tool to make sure they match our design                                                                                                                                                                         |

|          | A spinmemory                      | desi <sup>B</sup> I                                                                                                                                                                                                                           |

|          | ≜ tapeout                         | Message #shuttle                                                                                                                                                                                                                              |

|          | ∆ tropic                          | ダ B I ↔ ↔ ⊘ h≡ ··· Aa @ ☺ Ø ▶   •                                                                                                                                                                                                             |

|          | # xs ↓ Unread mentions            |                                                                                                                                                                                                                                               |

## How do we simplify chip

## design? #2

© 2022 EFABLESS CORPORATION

## Codify and abstract knowledge

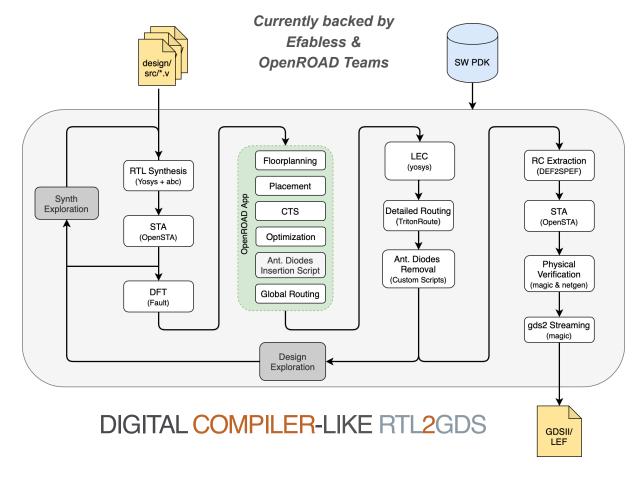

#### Automate code-to-chip like a *GNU software compiler*

It opens the door for software developers to generate hardware That's at least a 1000x more potential designers!

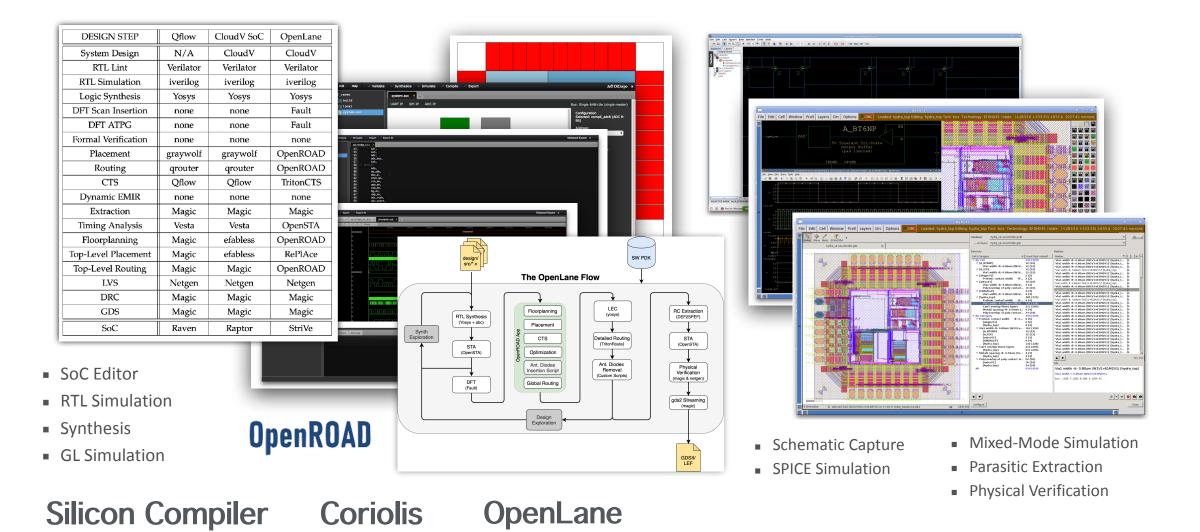

#### **OPEN SOURCE DESIGN FLOWS & TOOLS**

### Why does it matter to have tools

#### open-sourced?

## Limitless availability which fosters spontaneous idea realization and open collaborative development by community

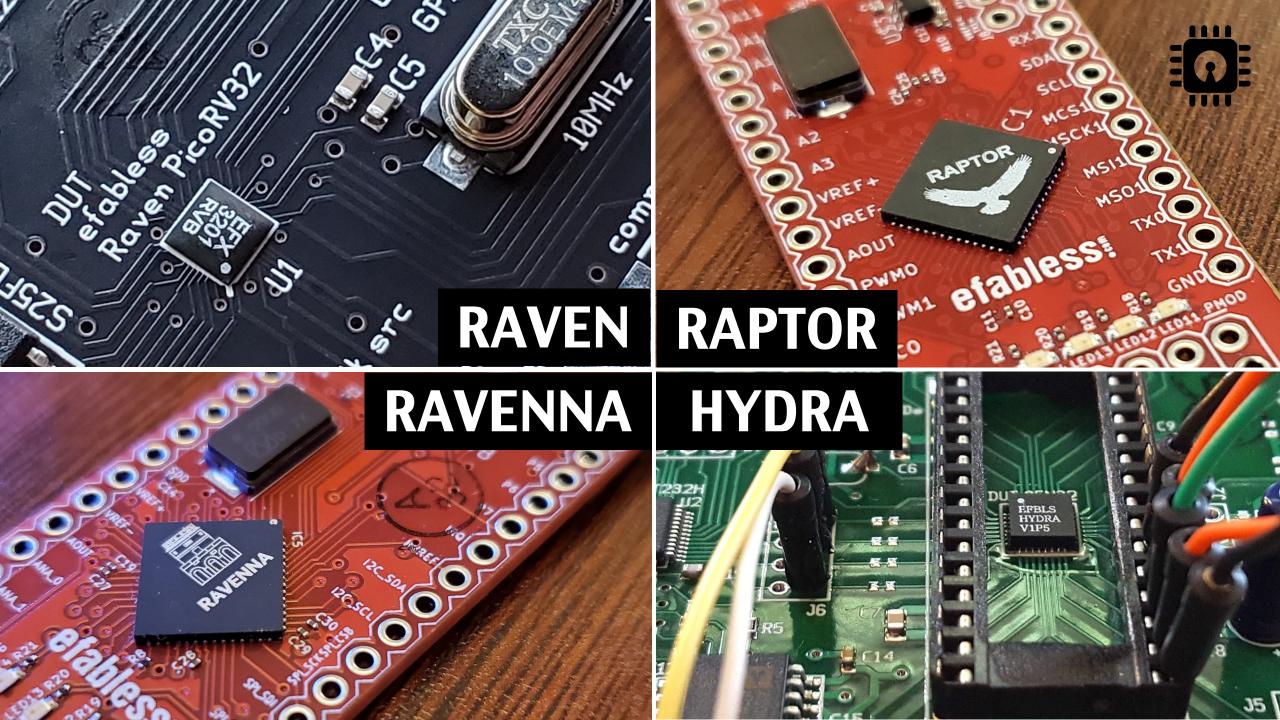

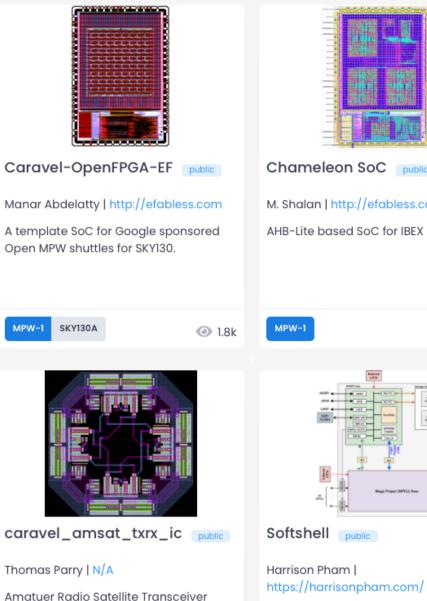

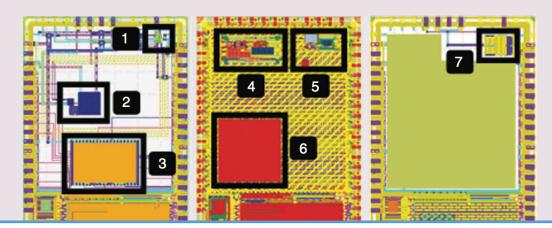

#### EXAMPLE OPEN SOURCE SoCs

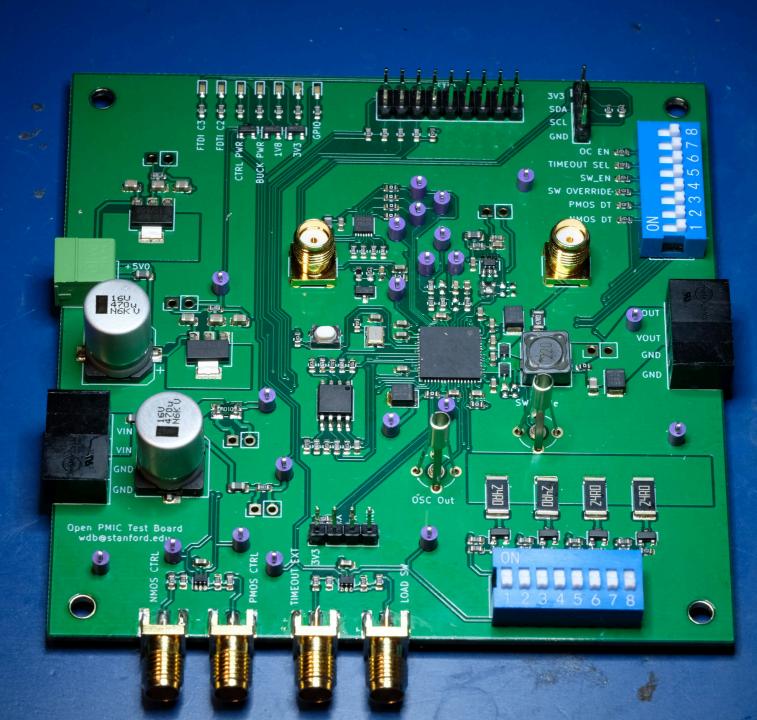

#### HYDRA REFERENCE ASIC

• A reference ASIC platform for testing A/MS IP modules

#### • Features

- Based on a standardized pad frame used for multiple core chip.

- Designed along with it's companion test PCB & test SW.

- Interfaces to a personal computer via USB.

- Top-level is available to community members to modify & re-shuttle.

- Intended as a design & test learning vehicle for analog/ms blocks

#### • Included IP modules

- 10-bit SAR ADC aadcc02

- 10-bit voltage-scaling DAC adacc02

- GP Low Power BGAP abgpc01

- GP AMP aopac01

- GP Bias Cell abiac01

- SPI Controller efdspi001

- Dynamic Power-on-Reset aporc01

- LP CMOS Comparator acmpc01

- 14KHz RC Oscillator arcoc01

- 1-6MHz Crystal Oscillator axtoc01

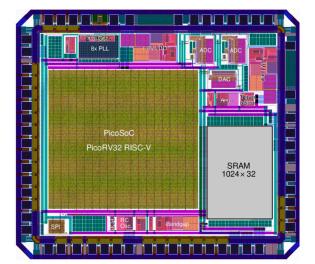

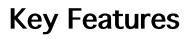

### RAVEN - 32-bit RISC-V uC

- RISC-V CPU (PicoRV32)

- SRAM 32x1024

- 100 MHz clock rate

- Programmable clock source

- 16 channels GPIO

- 2 ADCs

- 1 DAC

- 1 Comparator

- Over-temperature alarm

- 100 kHz RC oscillator

- Programmable functions on GPIO outputs

- Programmable interrupts on GPIO inputs

### http://github.com/efabless/raven-picorv32

etabless<sup>1</sup>

**Chip Description**

EFX3201 RISC-V SOC

**iCE40UP5K** An ultra-low power FPGA

AT25SL321 A serial interface Flash memory device

SIT8021 The industry's smallest and the lowest power MHz oscillator.

W25Q80D A serial Flash memory

GEM2 is a RISC-V based heterogeneous, chip scale system integration solution targeting edge AI consumer electronics, industrial IoT, medical devices and mobile application. GEM2 consists a series of chiplets that, along with zGlue Smart Fabric, incorporates of iCE40 FPGA and Efabless Raven RISC-V chip which reduces the barrier of developing a custom SOC. It's tiny, secured and fast time to market.

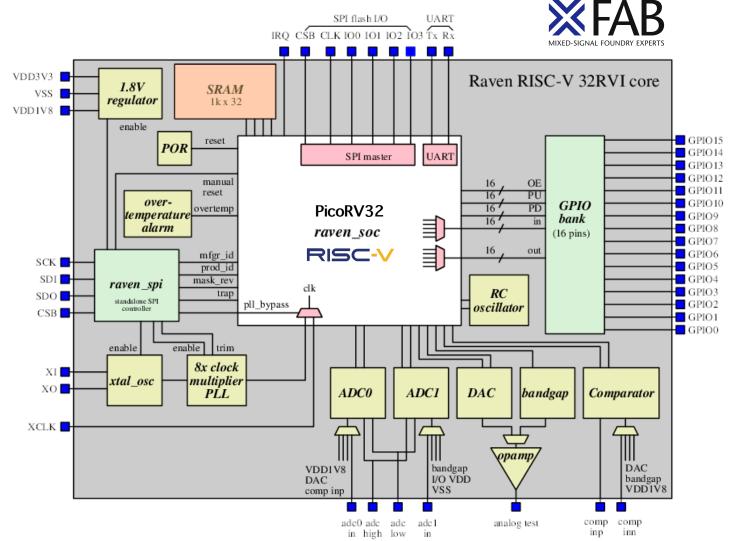

### RAVENNA - 32-bit RISC-V uC

### **Key Features**

- RISC-V CPU (PicoRV32)

- 2 10-bit SAR ADCs

- 1 10-bit DAC

- 1 analog comparator

- 1 100kHz RC oscillator

- 1 1.235V band gap reference

- 1 high temperature alarm

- 1 QSPI flash controller 1 UART

- 1 SPI master

- 1 I<sup>2</sup>C master

- 1 counter-timer

- 16 general-purpose digital input/output channels

- 4k word (4096 bytes × 32 bits) on-board SRAM

- 136 (128) word (128 bytes × 32 bits) on–board NVRAM

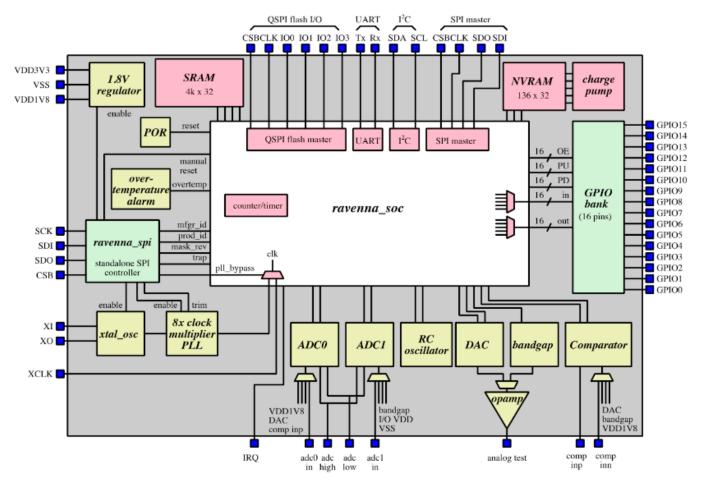

Example Of Commercial Interest in Open Source ASIC Design

Open Source Based Privacy Protection for IoT

Observation General Purpose Analog Functions can do the job

NEC

# Designed and Verified with 100% Open Source Tools

RAPTO

35

õ

R

oven

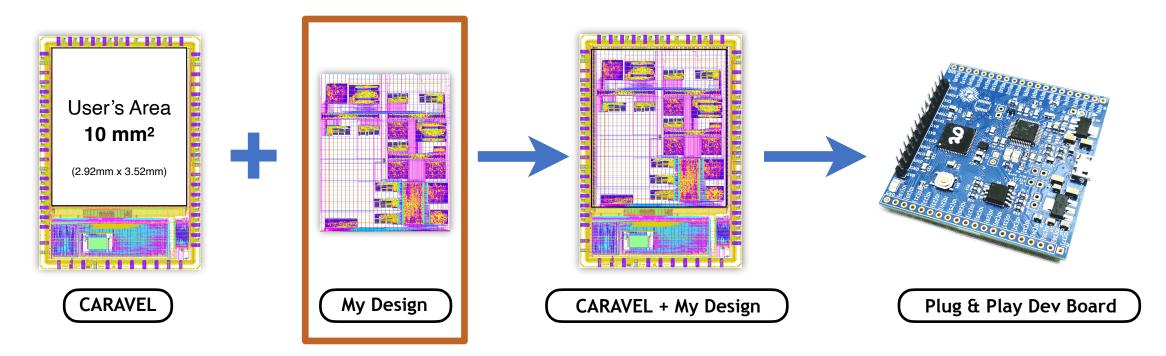

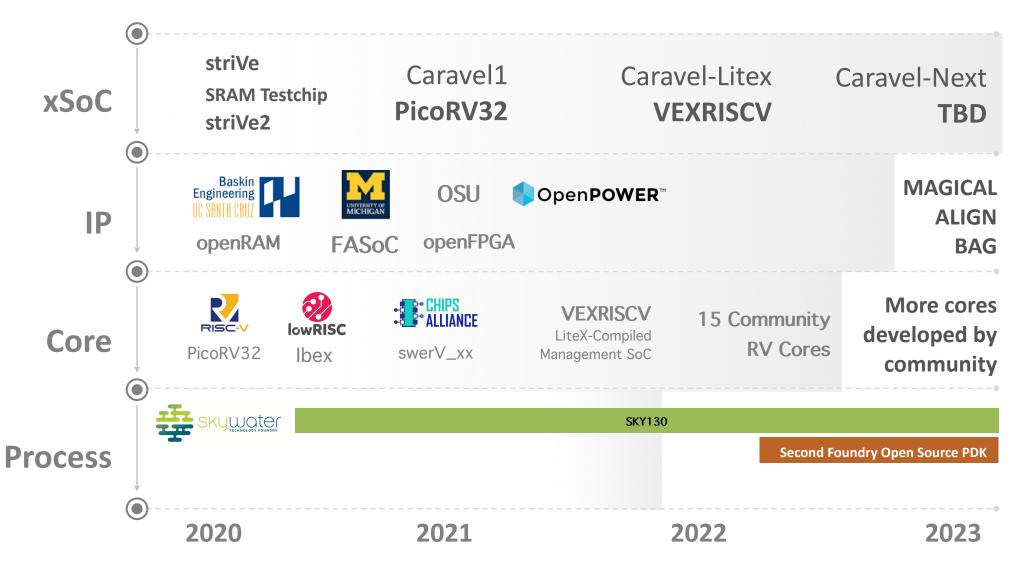

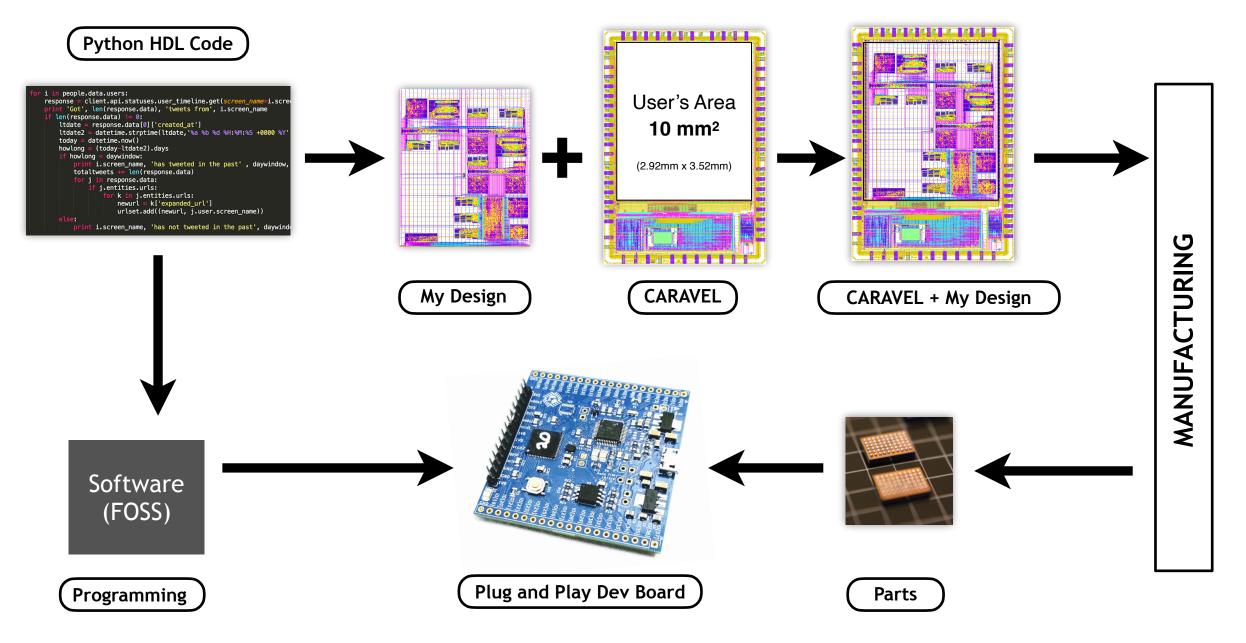

# How do we simplify chip

# design? #3

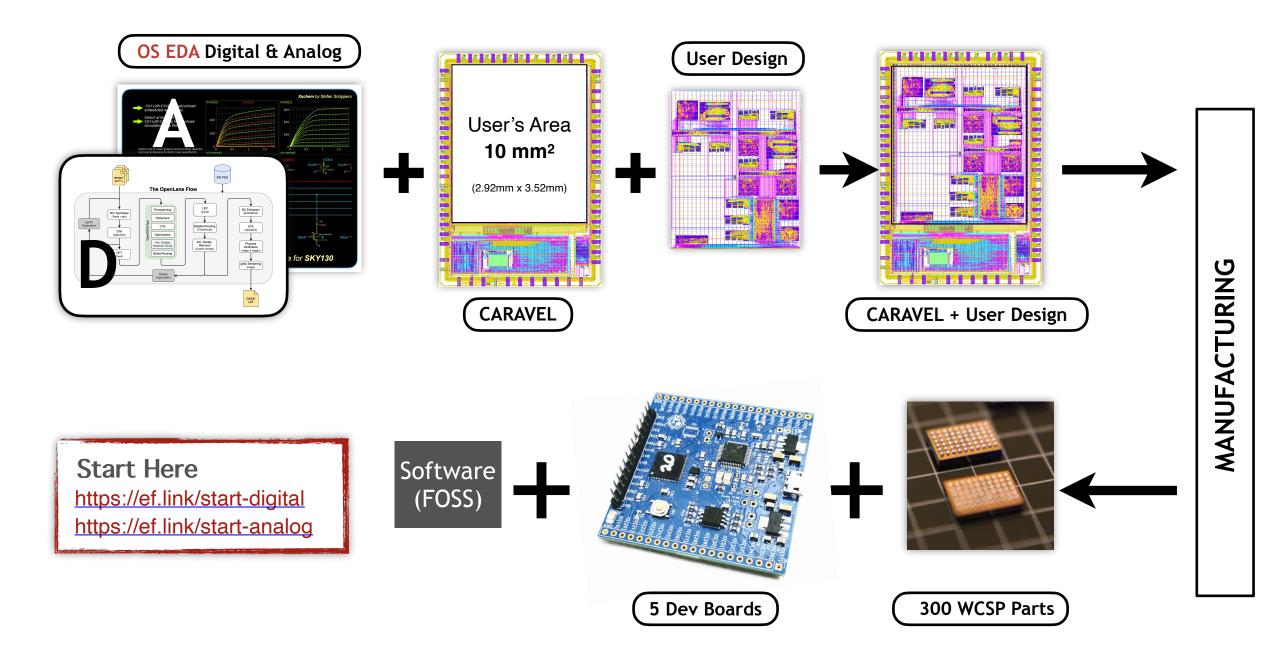

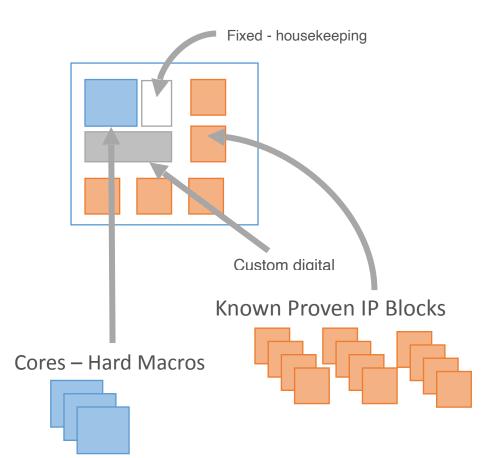

# Start from the 15th floor to reach 20

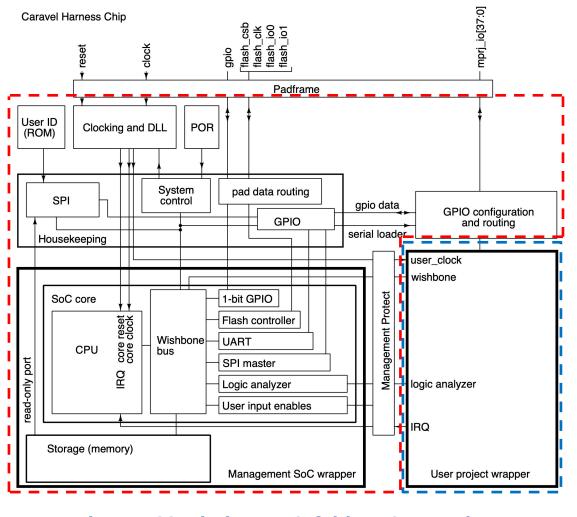

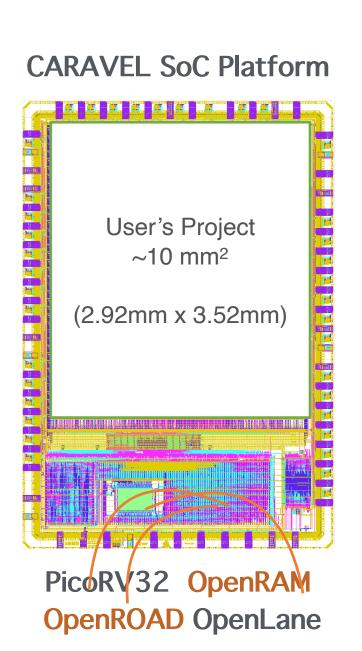

Build on existing foundational work by others - **CARAVEL** You only need to know your design ... or **your code**

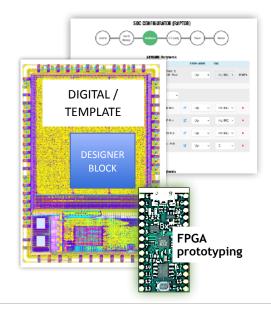

### **CARAVEL** PLATFORM

### https://github.com/efabless/caravel

efabless:

#### © 2022 EFABLESS CORPORATION

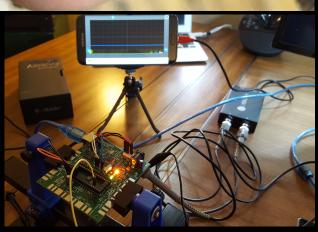

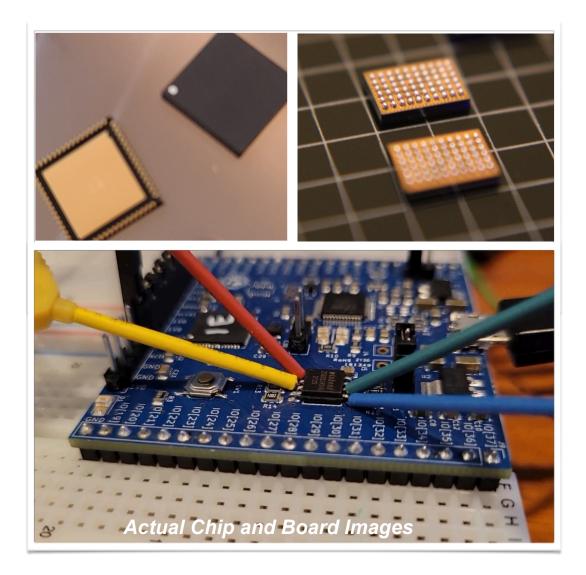

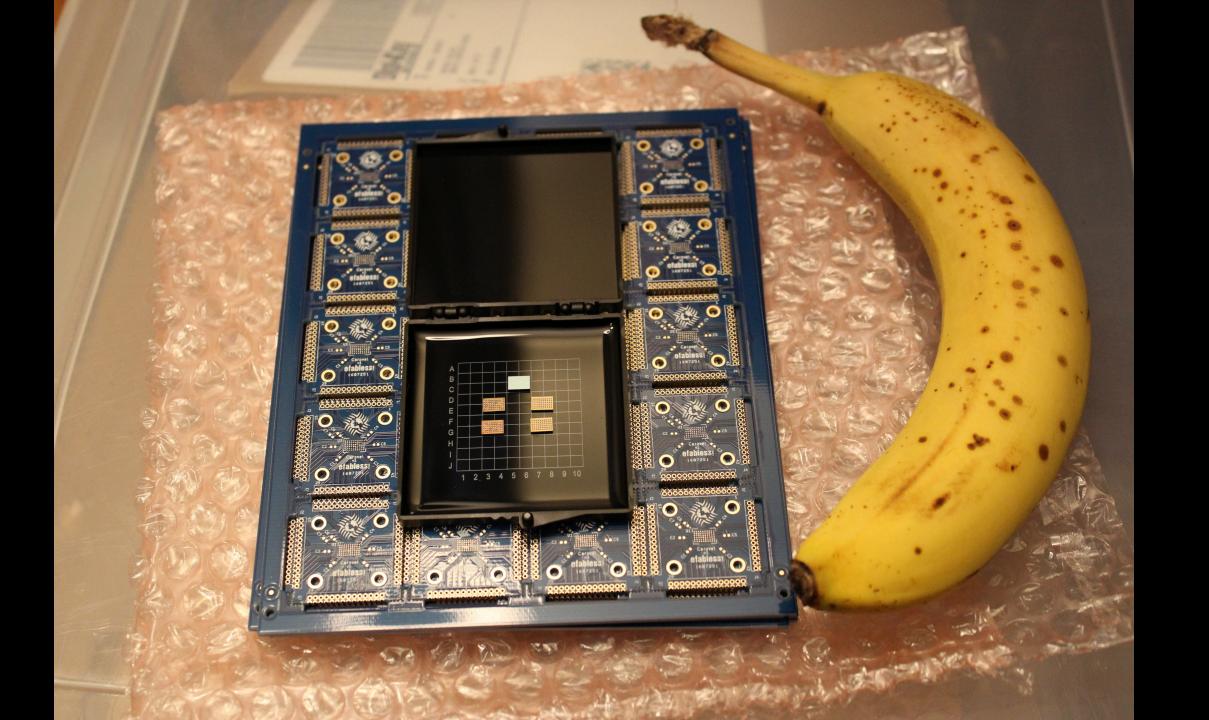

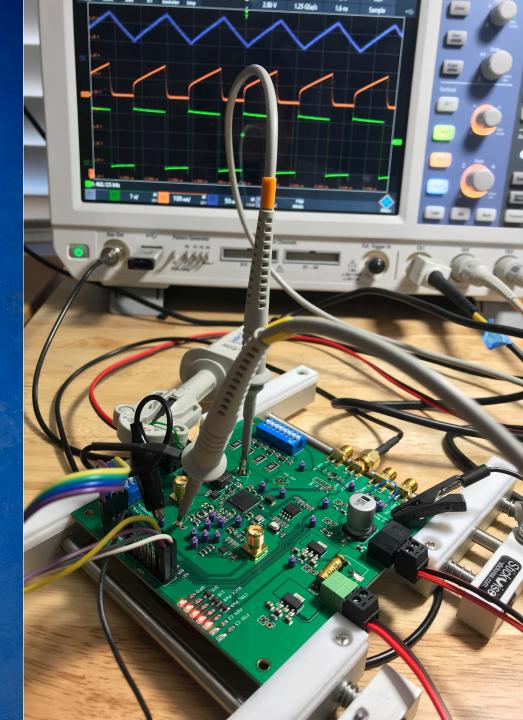

### **SILICON TESTING & VALIDATION**

### Designers receive **packaged chips** and **assembled 5 evaluation boards** with for each project

### On-chip **open source** test framework with firmware to support the following:

- On-chip logic Analyzer

- Drivers for common peripherals

- Flash memory programming software utility

- Example firmware routines for common functions

- Instructions for customizing firmware for each project

# How do we simplify chip

# design? #4

© 2022 EFABLESS CORPORATION

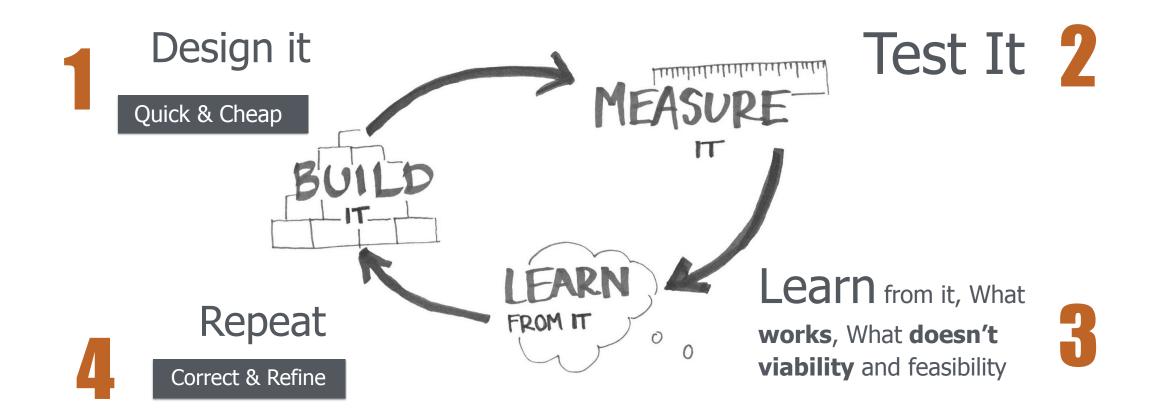

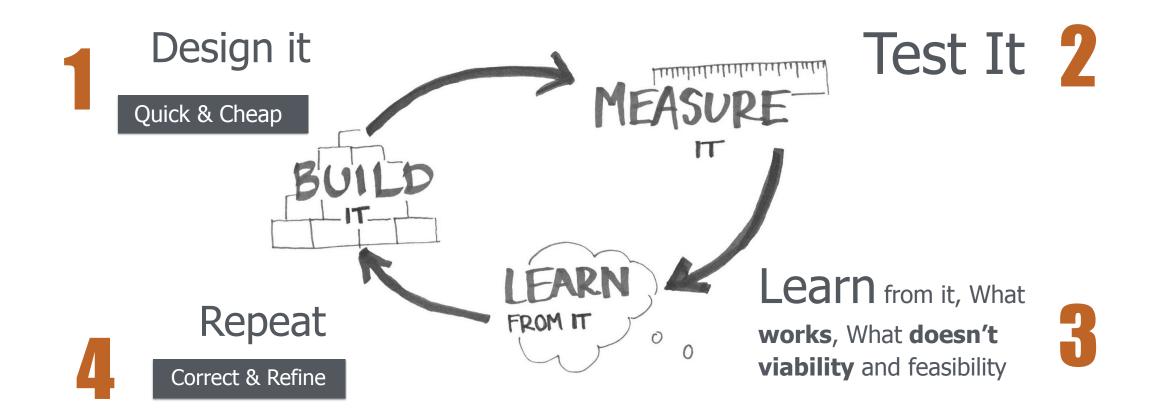

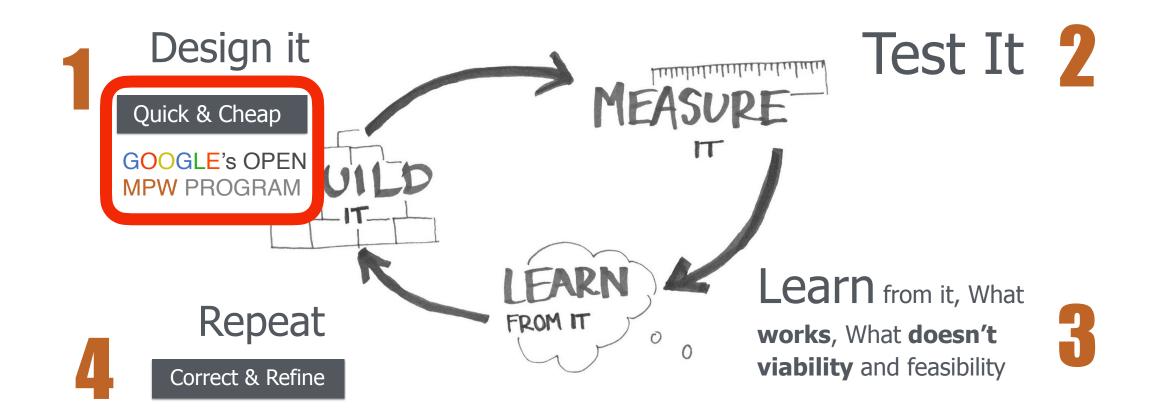

# Enable — Fail fast, learn and repeat

# OK - sounds good but ... hardware iterations cost \$\$

# Enable — Fail fast, learn and repeat

# Enable — Fail fast, learn and repeat

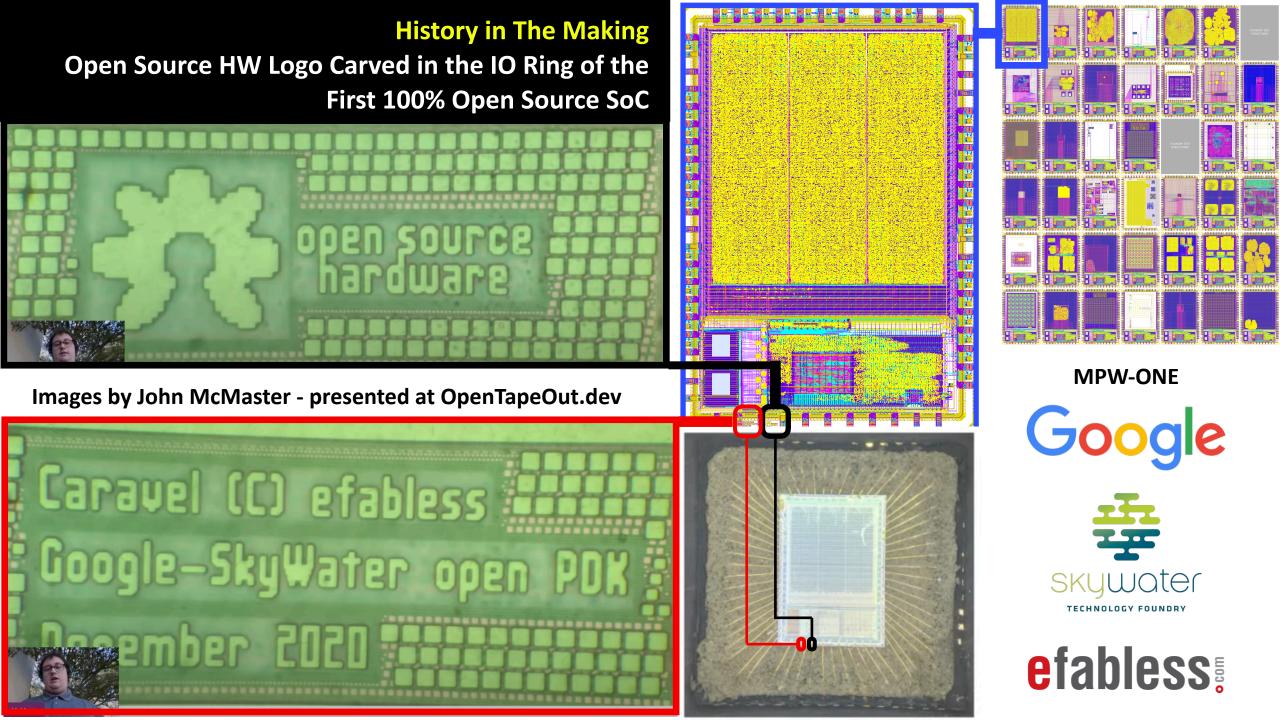

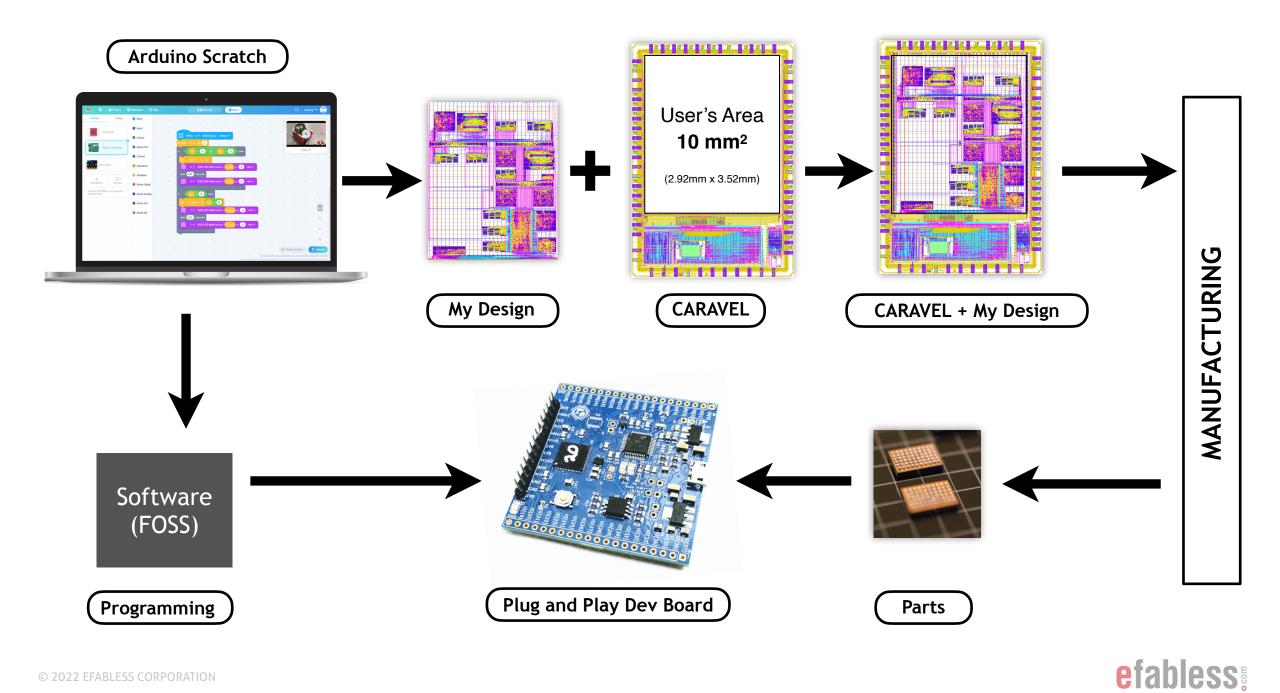

### FREE SILICON SPONSORED BY GOOGLE

- **Google** is funding **4** manufacturing runs in **2022**

- A minimum of 40 designs each run

https://ef.link/gmpw

here

Start

- Participants use a Harness SoC (<u>Caravel</u>) 10mm2 open area

- Use <u>SKY130</u> process & OS Digital & Analog Design Tools

- Participants get 5 dev boards + 300 WCSP-packaged parts

- All designs must be public and under an open source license

- All designs must contain information & files to *reproduce the work*

- You are strongly encouraged to try new ideas, *take risks and iterate*

- All skill and experience levels are welcome to participate

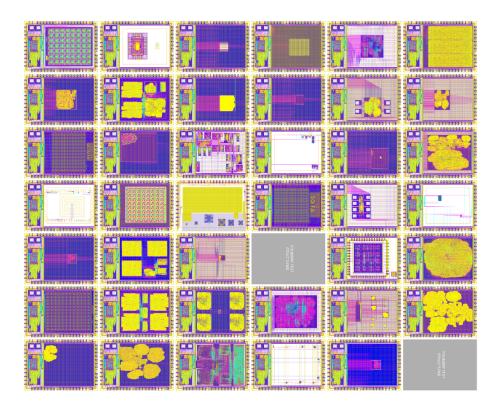

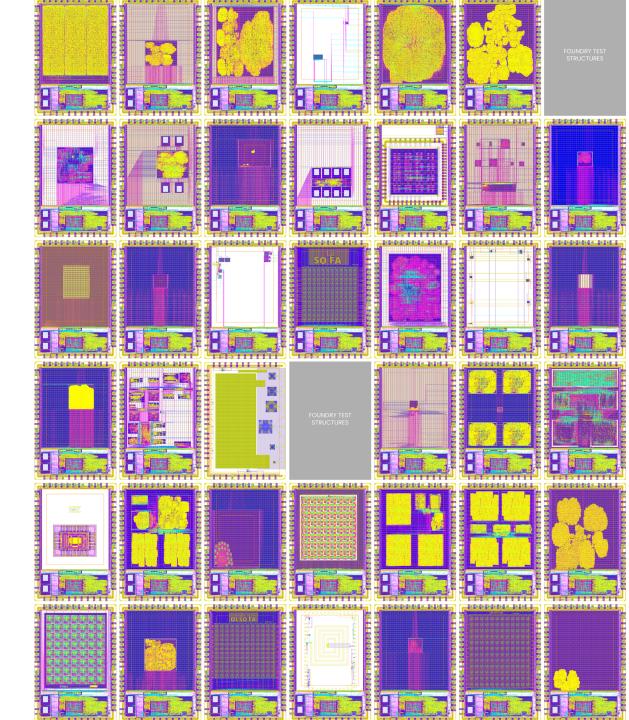

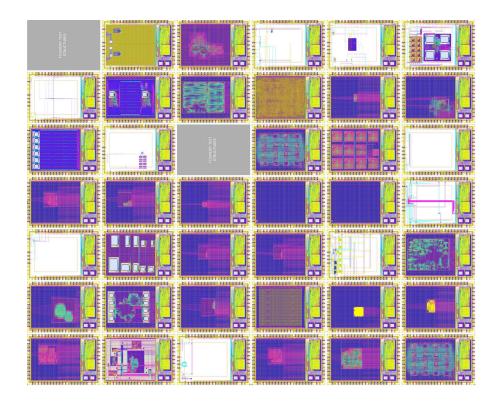

The first shuttle was overbooked: 45 designs submitted in 30 days!

### **DESIGN TYPES**

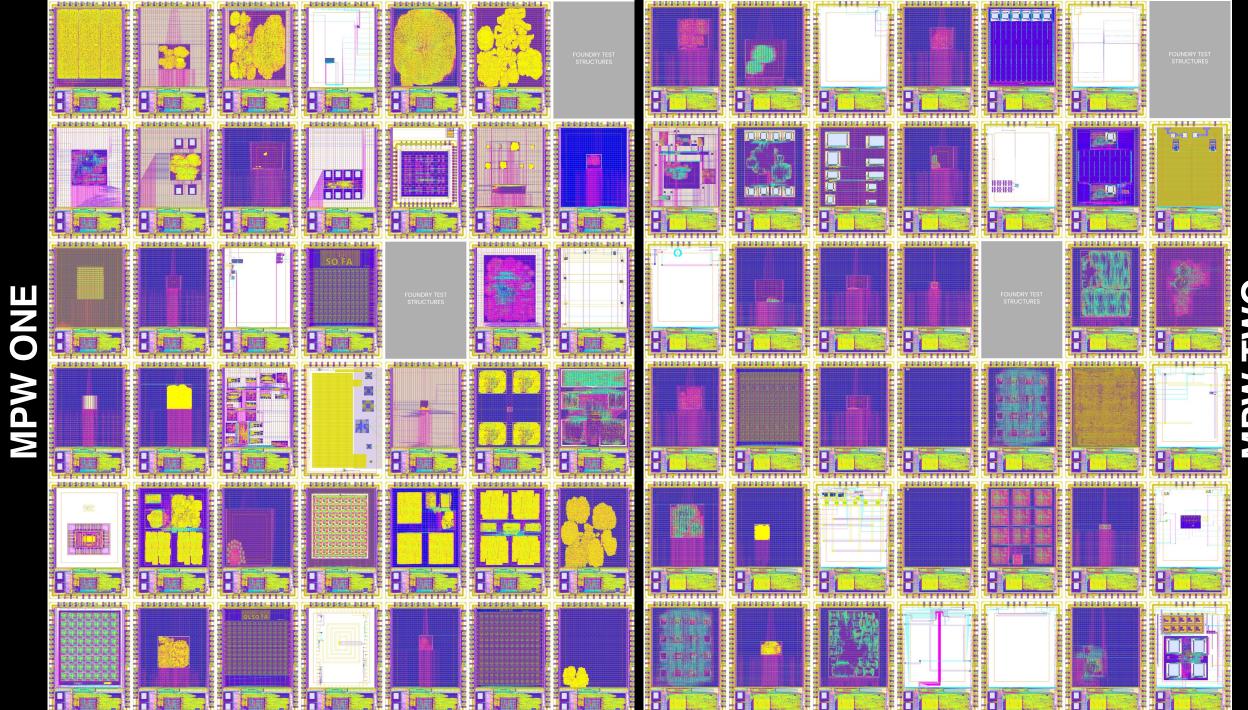

MPW ONE

**efabless**

Sponsored by

- 9 x Open processor cores

- 9 x SoC's

- Crypto-currency Miner

- Robotic App Processor

- Amateur Satellite Radio Transceiver

- 7 x Analog/RF

- 5 eFPGA's

### **DESIGN TYPES**

- 9 x Open processor cores

- 9 x SoC's

- Crypto-currency Miner

- Robotic App Processor

- Amateur Satellite Radio Transceiver

- 7 x Analog/RF

- 5 eFPGA's

### COMPANIES

- IBM: OpenPOWER MicroWatt

- QuickLogic eFPGA

- Antmicro

- Western Digital Swerv-EL2

- EFabless

- SpinMemory

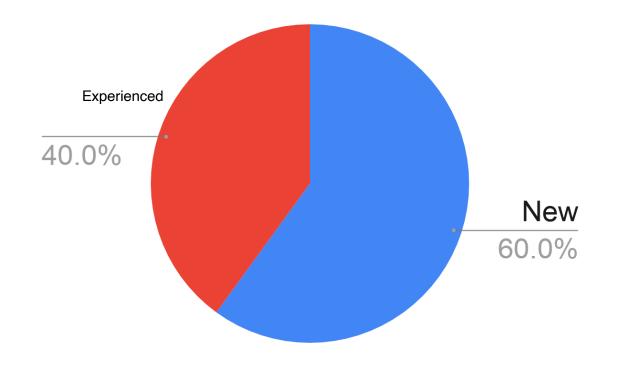

# 60% by first time designers!

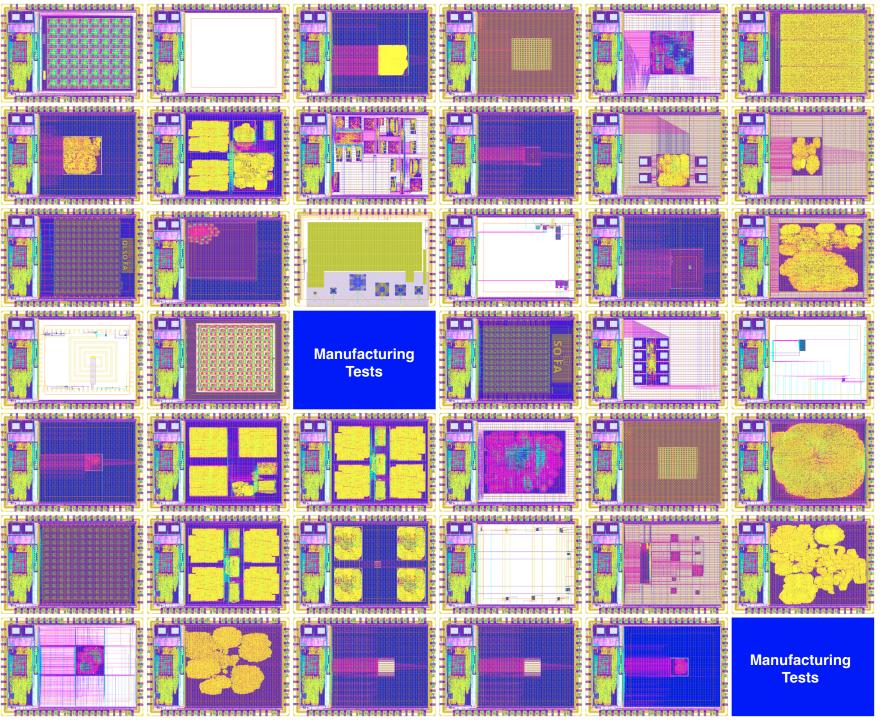

And so was the second: 56 designs submitted in 30 days!

### **DESIGN TYPES**

- 11 x Open processor cores

- 11 x SoC's

- Crypto-router

- T2D Converter LIDAR

- Multi-project harness for Caravel x 16

- 17 x Analog/RF

- 2 eFPGA's

**efabless**

Sponsored by

Google

**MPW TWO**

MPW TWO

### **SRAM** Characterization

And Anthen

### SRAM Test Chip

001

S/N:

Property and sold

DUT\_VCORE

By: Andrew Zonenberg

# terizatio SRAM Charact

15

ω.

S/N: 004

111

DHUATRON

88

Contro

Temperature

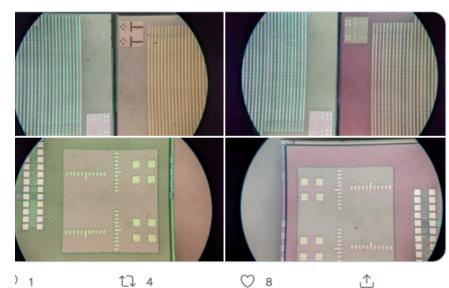

- www.zerotoasiccourse.com/post/mpw1-bringup/

- github.com/mattvenn/mpw1-bringup

bit.ly/cicc22-edu-goog

Slide provided by: Tim Ansell

### All my ASIC designs for Google MPW1 are working!

Zero To ASIC Course 1.1K views • 1 month ago

### youtu.be/IdOvywOSSmI

Matthew Venn @matthewvenn · Mar 31 Still can't quite believe I have a clock on my desk that is powered by a chip I designed!

### bit.ly/cicc22-edu-goog

Slide provided by: Tim Ansell

### Volodymyr Pikhur @vpikhur · 15h

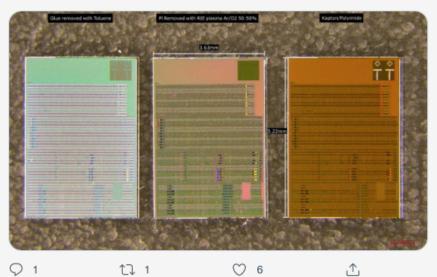

...

#### olodymyr Pikhur @vpikhur · 15h

ter polyimide is removed there is adhesive/glue layer remaining. Adhesive In't be removed with normal solvents such as acetone or isopropyl cohol. Very non-polar solvent such as Toluene does the job.

Volodymyr Pikhur @vpikhur · 15h

All 3 under stereo microscope with approximate die dimensions.

### Replying to @vpikhur

Loaded 10 samples into RIE (reactive ion etcher) to strip top polyimide layer. I use a 50/50 mix of oxygen and argon gas.

Q1 1 1

<u>`</u>↑,

...

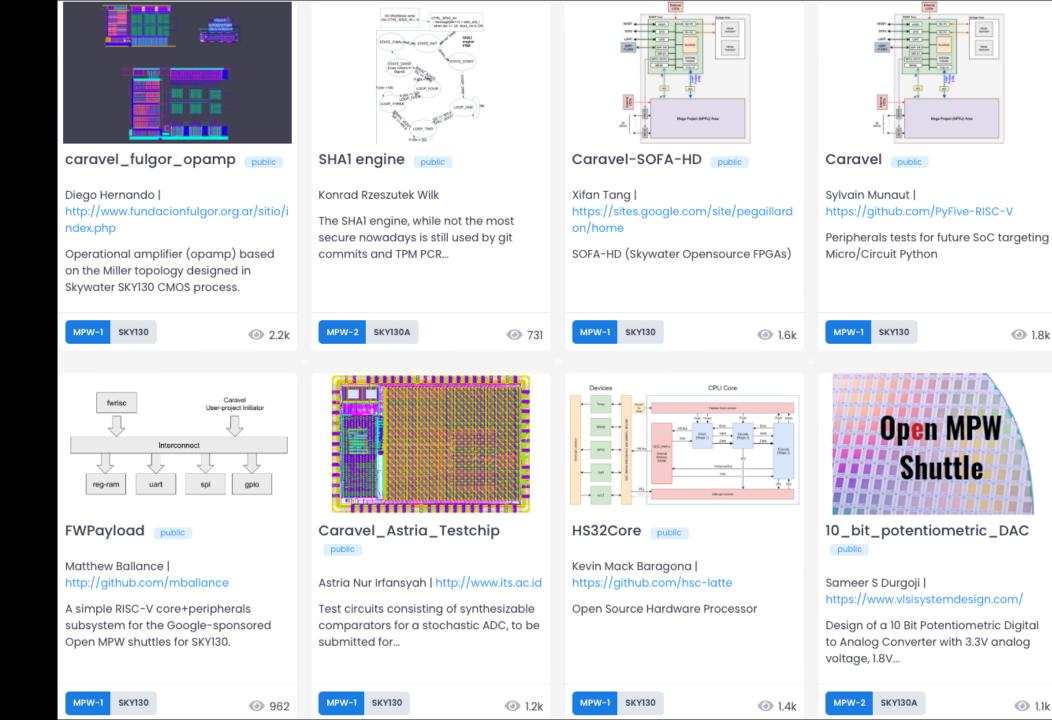

# **OpenMPW Project Submissions**

### **Always Overbooked**

# **45 56 52 55 77** MPW-1 MPW-2 MPW-3 MPW-4 MPW-5

https://efabless.com/projects

# How do we simplify chip

# design? #5

© 2022 EFABLESS CORPORATION

# Build an open library of "blocks"

### Make them like **LEGO**

- Silicon proven / verified functions

- Highly leveraged known proven IP blocks

- Scope of customization is constrained

- Quality processes enable extending the known proven IP blocks by community

1.1k

1.8k

10ya Despet

public

SKY130

SKY130A

**Open MPW**

Shuttle

Caravel-SOFA-CHD public

Xifan Tang | https://sites.google.com/site/pegaillard on/home

SOFA-CHD (Skywater Opensource FPGAs)

Caravel public

MPW-1

M. Shalan | http://efabless.com

NFive32-Based SoC to validate several open-source projects and IPs.

| ourur                |                                          | _000       | public             |

|----------------------|------------------------------------------|------------|--------------------|

| James S<br>https://v | tine  <br>Isiarch.ece                    | n.okstate. | edu/               |

| impleme              | _RISCV_OS<br>entation of<br>or inside of | a single-c | ycle RISC-V<br>vel |

| MPW-1                | SKY130                                   |            | 1.2k               |

|                      |                                          |            |                    |

| Morph                | lelogic                                  | aublia     |                    |

10ym 10ya Despet

Mana Period (MPD.) Ave.

Caravel\_RISCV\_OSU public

- MorphleLogic public

- Merik Voswinkel | http://www.fiberhood.org

A test-wafer for testing Mophle Logic reconfigurable hardware for SKY130.

(SKY130) - Caravel Submission

1.4k

917

MPW-1

SKY130

| MPW-1 | SKY130 |

|-------|--------|

|-------|--------|

1.4k

2.8k

SKY130 MPW-1

Multicore MCU for implementing

software defined peripherals.

1.7k

1.2k

Silya Isaiper

APR-3 Ave

### OPEN SOURCE ECOSYSTEM AT WORK

# But there is always more... Jump in and contribute

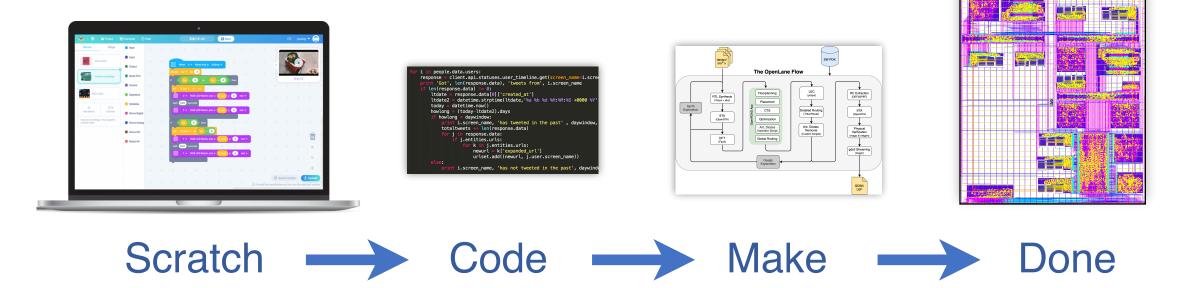

# How do we simplify chip

# design? #6

© 2022 EFABLESS CORPORATION

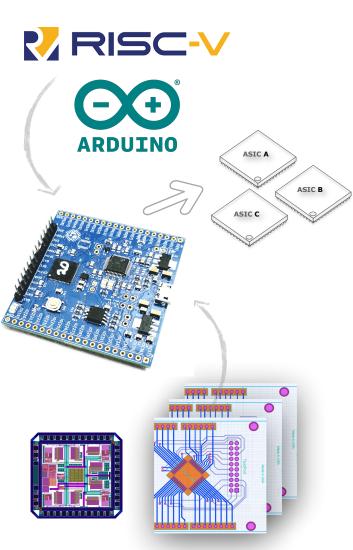

# Abstract access to knowledge

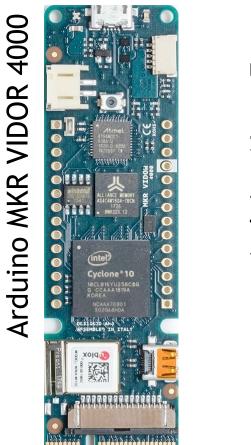

### Think Arduino $\bigcirc$

### Use graphical tools or code

© 2022 EFABLESS CORPORATION

efabless:

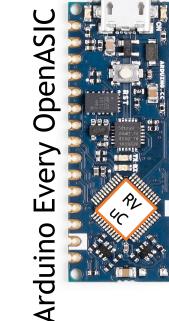

# ARDUINO PROTOTYPING SHIELD

• Simplified ASIC platform for prototyping - Arduino Shield

#### • Features

- Based on a standardized pad frame used for multiple core chip.

- Designed along with its companion test PCB & test SW.

- Interfaces to a personal computer via USB.

- Top-level is available to community members to modify & re-shuttle.

- Intended as a design & test learning vehicle for analog/ms blocks

### • Included IP modules

- 10-bit SAR ADC aadcc02

- 10-bit voltage-scaling DAC adacc02

- GP Low Power BGAP abgpc01

- GP AMP aopac01

- GP Bias Cell abiac01

- SPI Controller efdspi001

- Dynamic Power-on-Reset aporc01

- LP CMOS Comparator acmpc01

- 14KHz RC Oscillator arcoc01

- 1-6MHz Crystal Oscillator axtoc01

# BUT ....

What if I do not want to open source my design?I would like to guarantee my spot on the run.I need it on my own schedule.

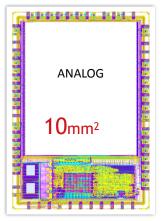

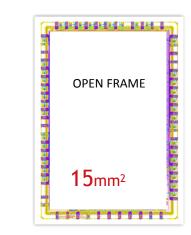

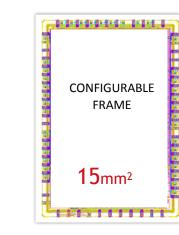

# chiplgnite OPTIONS

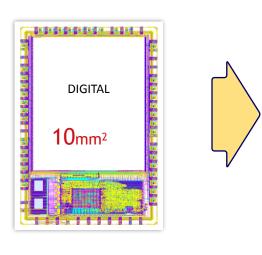

*IP* Development Digital & low frequency analog Enabling larger designer base

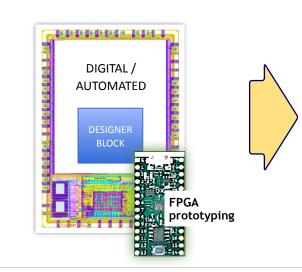

### HIGH COMPLEXITY

IP Development Complete Custom ASIC Analog & Digital Expert designer base

# chiplgnite USERS

Stanford **EE272** Design Course

Three more universities ....

High Schools coming in June 2022

### **Startups**

Using chipIgnite as their proof-ofconcept or low volume production

© 2022 EFABLESS CORPORATION

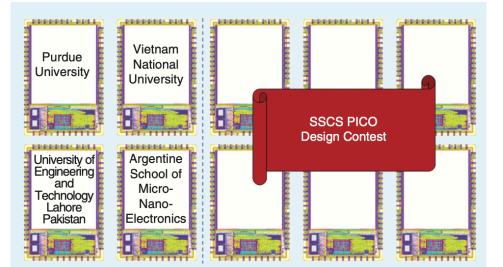

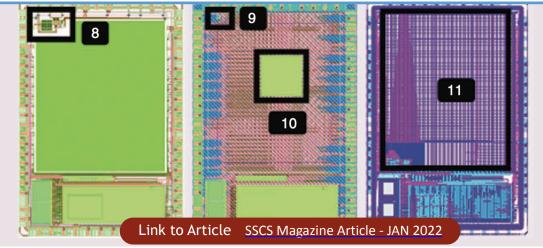

SSCS "**PICO**" Open Source Design Contest:

# 56+ submitted designs10 will tape out at Efabless

https://sscs.ieee.org/about/solid-state-circuits-directions/sscs-pico-program https://efabless.com/projects/project\_definition/SSCS-21

If you are a student and Want to learn .. how to Tapeout a chip ...?? Your own chip ... at a very low cost ... please join!!

Open Source FPGA Foundation global program innovation among university students

### 2 ChipIgnite Slots per University

Turkey, Pakistan, India, Australia

**IEEE - PICO PROGRAM**

### Multiple Projects per One chiplgnite Slot

# ~ \$10K ... still **not** a small number ...

# Crowdfund it ...

# ... or Community-fund it

### Write up your Idea

Go to GroupGets.com or CrowdSupply.com

Start a campaign at no risk - see example <u>CLEAR</u>

If your design gets funded (supported by the community)

then you got your own board with your custom ASIC

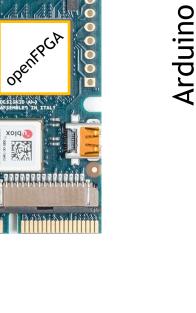

#### CLEAR - The Open Source FPGA ASIC - by chipIgnite

Single-unit price: **\$74.99** + shipping

CLEAR

#### **Product Details**

#### Name

Details

CLEAR - The Open Source FPGA ASIC - by chipIgnite

#### Brand / Manufacturer

Efabless Corporation

#### Details Discuss Updates

#### **Product Details**

Name CLEAR - The Open Source FPGA ASIC - by chipIgnite

Brand / Manufacturer Efabless Corporation

Manufacturer Part #

CI00025

**Product Description**

#### $\ensuremath{\textbf{CLEAR}}$ - The Open Source FPGA ASIC

POWERED BY

chiplgnite Rapid IC Creation

CLEAR is an Open Source FPGA ASIC delivered to you on its development board and its open source software development tools and all the ASIC design tools used to create it. That's for you to create your own - yes that's right - ASIC.

CLEAR is utilizing <u>Caravel</u> - the open source ASIC platform provided as a base System on Chip (SoC) provided by Efabless' <u>chip/gnite</u> offering.

#### What we will do

- 1. Generate an embedded FPGA macro based on the famous <u>OpenFPGA</u> generator framework

- 2. Integrate the eFPGA macro into *Caravel* which makes it an FPGA ASIC Clear

- 3. Manufacture the ASIC through chipIgnite program through <u>SkyWater Technology</u>

- 4. Package and mount the ASIC on its development board

- 5. Test the boards before you get them along with the open source FPGA programing software

- 6. You receive your board and have fun!

As part of the campaign we will show you *everything* we do including how to design *your own ASIC* with open source ASIC design software and how you can create a campaign just like this one for your own custom ASIC. All that without having to make a giant hole in your pocket for ASIC design and manufacturing.

## ..... that's how its done ....

Creating a World where a 14-year-old Designs a Chip

# The time is now

### Get Involved - Useful Links / Repos

### **Information Hub**

### github.com/efabless/skywater-pdk-central

- Join SkyWater PDK Slack Space https://join.skywater.tools

- The OpenLane flow for digital PnR can be found at https://openlane.io

- The OpenROAD Project https://theopenroadproject.org/

- The documentation is at https://docs.skywater.tools

- MPW-ONE https://efabless.com/open\_mpw\_shuttle\_project\_mpw\_one

- Caravel documentation https://caravel-harness.readthedocs.io/en/develop/index.html

- WOSET/ICCAD Workshop on EDA https://woset-workshop.github.io/WOSET2020.html

# Supporting Slides

# chiplgnite

FOR UNIVERSITIES

### Undergraduate courses Capstone projects Graduate Research

### TAPE-OUT COURSES

Analog and / or Digital Design Courses

### • Two-session courses:

### • Single session courses:

- Design + test via FPGA

- Design + test previous student project

- Test broken design + fix and tapeout

- Future: one course period design/tape-out/test

## .... what we need ...

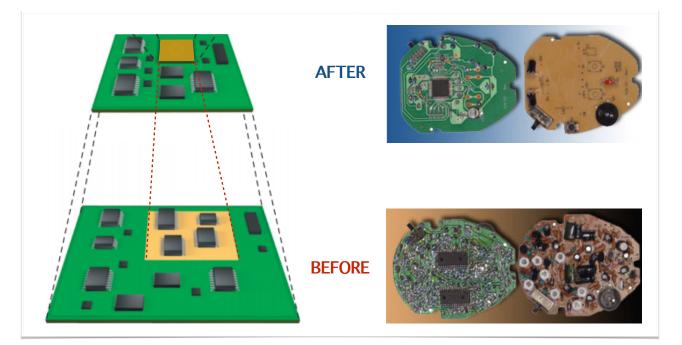

Why Care to have your own ASIC for your product?

□ Reduce cost in your overall application

Optimize performance and power efficiency via integration

Reduce the size and enable superb Product Design

Protect Intellectual Property through hardware embedding

Mohamed MK @mkkassem · Apr 14 Caravel bring up day at Stanford. Go EE272B Team!!

#chipIgnite #sky130 #caravel #opensourcechips

个

photos.google.com Stanford - EE272B - ChipIgnite One 84 new items added to shared album

**1**] 4

### Woowzaaa!! I'm Caravel !!

bit.ly/cicc22-edu-goog

$\bigcirc$

| ₩ WaveForms (new workspace) |          |    |         |          |            |          |            |             |         |                |               |                                                              |         |          |         |           |          |           |

|-----------------------------|----------|----|---------|----------|------------|----------|------------|-------------|---------|----------------|---------------|--------------------------------------------------------------|---------|----------|---------|-----------|----------|-----------|

|                             |          |    |         |          |            |          |            | Welcom      | e 🔶     | Help 🕲 Scope   | 1 🕨 🛞 Logic 1 | Wavegen 1                                                    | •])     |          |         |           |          | 88        |

| V                           | iew Wind | ow | _       |          |            |          |            |             |         |                |               |                                                              |         |          |         |           |          | 6         |

|                             | Sto      | -  | Mode:   | Repeated | 0          | Trigger: | Normal     | 0           |         | Simple         |               | Pulse                                                        |         |          |         | Position: | 9.002 us | S         |

|                             | 0.00     | P  | Buffer: | 10       | 0 🕂        | Source:  | Digital    | 0           | Inputs: | 100MHz DIO 015 |               |                                                              | 0       |          |         | Base:     | 2 us/div | -         |

| N                           | • Т      |    |         |          |            |          | -          |             |         |                |               |                                                              |         |          |         |           |          |           |

| •                           |          | т  | Armed   | Name: F  | LASH IN PO | osition: | 0.00000404 | s Value: h( | 3       |                |               |                                                              |         |          |         |           |          | L L E Q Q |

| т                           | 8        | 1  |         | hFF      | Н          | hFF      |            | hFF         | hFF     | hFF            | hFF           | h93                                                          | h00     | h00      | h00     | ? ht      |          |           |

|                             | *DIO     | 0  |         | 1        | Π          |          | Π          |             |         | 2              |               |                                                              |         |          |         |           |          |           |

|                             | •DIO     | 1  |         |          |            | זחחחר    |            | www         | ΠΠΠΠ    | ппппппп        | ппппппп       |                                                              | 1000000 |          | www     |           | 10       |           |

|                             | DIO      |    |         |          |            | 0000     |            |             |         |                |               |                                                              | 1 []]   |          |         | Π         |          |           |

|                             | 8        | 2  |         | hFF      | Н          | hAB      |            | h03         | h00     | h00            | h00           | h00                                                          | h00     | h00      | h00     | ? h(      | <u> </u> |           |

|                             | *DIO     | 0  |         | 1        | Π          |          | П          |             |         | 0.0            | -             |                                                              |         |          |         |           |          |           |

|                             | •DIO     | 1  |         |          |            | ากกก     | บากก       | ากกกกก      | תתתת    | ากกกกกก        | תתתחתתת       | MMMMM                                                        | ากกกกกก | กกกกกกกก | ากกกกกก | เกกกกก    | 10       |           |

|                             | DIO      |    |         |          |            | ŪΓ       |            | ]           |         | 000            |               |                                                              | 100     |          |         |           |          |           |

|                             | DIO      |    |         |          |            |          |            |             |         |                |               |                                                              |         |          |         |           |          |           |

|                             |          |    |         |          |            |          |            |             |         |                |               |                                                              |         |          |         |           |          |           |

|                             |          |    |         |          |            |          |            |             |         |                |               |                                                              |         |          |         |           |          |           |

|                             |          |    |         |          |            |          |            |             |         |                |               |                                                              |         |          |         |           |          |           |

|                             |          |    |         |          |            |          |            |             |         |                |               |                                                              |         |          | -       |           |          |           |

|                             |          |    |         |          |            |          |            |             |         |                |               |                                                              |         |          |         |           |          |           |

|                             |          |    |         |          |            |          |            |             |         |                |               |                                                              |         |          |         |           |          |           |

|                             |          |    |         |          |            |          |            |             |         |                |               |                                                              |         |          |         |           |          |           |

|                             |          |    |         |          |            |          |            |             |         |                |               |                                                              |         |          |         |           |          |           |

|                             |          |    |         |          |            |          |            |             |         |                |               |                                                              |         |          |         |           |          |           |

|                             |          |    |         |          |            |          |            |             |         |                |               |                                                              |         |          |         |           |          |           |

|                             |          |    |         |          |            |          |            |             |         |                |               |                                                              |         |          |         |           |          |           |

|                             |          |    |         |          |            |          |            |             |         |                |               |                                                              | D       |          |         |           |          |           |

|                             |          |    |         | D'Lee    |            |          | 61         |             |         |                |               | กล่างเป็นกลังกลังกล่างเป็นแปลแปลแปลเป็นแปลเป็นเป็นเป็นเป็นไป | å       |          |         |           |          |           |

|                             |          |    |         |          |            |          |            |             | 7       |                |               | 10                                                           | -       |          |         |           |          |           |

|                             |          |    |         | E        |            |          |            |             |         |                |               |                                                              |         |          |         |           |          |           |

|                             |          |    | D.      |          | age and    | - Cr     |            |             |         | 1 60           |               |                                                              |         |          |         |           |          |           |

|                             |          |    |         |          |            |          |            |             |         |                |               |                                                              |         |          |         |           |          |           |

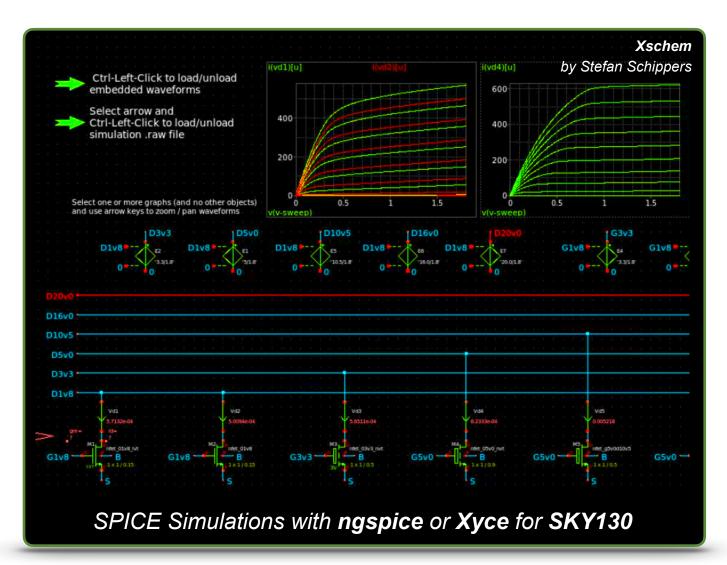

### ANALOG TRANSISTOR-LEVEL

Analog transistor-level design,

schematic and layout

Schematics: Xschem

Simulators: ngspice, Xyce

Support: Process Corners and statistical simulations

Packed with out-of-the-box examples - just click, copy and run yours

### ARDUINO ASIC/SoC - WHAT - just thoughts

161